这是一份本人10年经验总结的一份数字芯片设计后端PR的脚本,比较全面各个部分都有涉及,脚本是ICcompiler模式下的PR脚本

”icc后端pr脚本 数字后端 数字后端总结 数字后端设计 数字设计icc“ 的搜索结果

ICC2的简单介绍和学习,不断更新。

数字IC后端设计实现应该如何快速入门?

数字IC后端实现40天速成篇(上)

标签: 后端

使用StarRC工具抽取ICC写出的电路网表中的寄生参数,接着,使用PrimeTime工具获得寄生参数信息后写出sdf(standard delay format文件),再将该文件反标入ICC的电路网表,输出仿真结果,此时后仿考虑了实际连线的RC...

如何才能成为数字IC后端ECO专家?

标签: 后端

数字IC后端实现40天速成篇(中)

标签: 后端

数字IC后端设计实现全流程解析

等后面没那么忙的时候,小编就抽空来整理一个清单,让大家循序渐进,系统地来学习数字后端设计实现的整个环节。so, 今天先跟大家聊聊数字 IC 设计中 ECO 的那些事。ECO 中文翻译就是工程变更(Engineering Change ...

2.设计流程以及各步骤 3.工程师进阶流程 4.需求数量 工作时间 1.四大岗位与技能要求 数字前端工程师:读写文档(function sspec \ design spec)、coding (verilog\c c++\RTL\SOC)、协议、debug、support 数字验证...

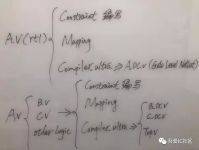

由于版本较为久远,并没有提到今年来出现的Fusion compiler,这是一个可以完成综合和PR的工具,功能相当于DCG+ICC2,后文后简单介绍。还少了一个lib转db的工具 Library compiler。另外会同时介绍STA工具PrimeTime;...

【数字IC基础】IC(Integrated Circuit,集成电路)常用缩写

系统设计是确定IC的算法模型和系统架构等,并通过一些高级语言、matlab等对算法模型进行仿真、架构评估,划分各个模块的具体功能,最终确定系统设计规格书。 三、RTL Coding 通过VHDL/Verilog对各个模块...

有时候想画一个环形或者不规则形状的metal shape/blockage,一遇到更新floorplan都要重新画,手工活如果能被脚本替代肯定是最优解,ICC2就提供这样的一组命令有效提高工作效率。

ICC2进行top level的PR工作时需要block level的ndm,ICC2可以直接调用PT extract model产生指定block的ndm,流程如下。 1)create_frame extract model前需要对指定block产生frame view。 2)环境设置 set_...

数字IC后端实现之物理验证Calibre LVS常见错误案例解析

芯片设计中的Makefile精简介绍 Makefile可以做什么? Makefile可以根据指定的依赖规则和文件是否有修改来执行命令。常用来编译软件源代码,只需要重新编译修改过的文件,使得编译速度大大加快。 ...

在英伟达,后端工程师主要分布在两个部门——VLSI 部门和ASIC 部门,前者主要做PR的工作,是所有fabless 公司纯正的后端部门;后者主要做综合、timing 的工作,在IC流程中也称之为中端部分。因为两者分工不同,所以...

推荐文章

- php 上传图片 缩略图,PHP 图片上传类 缩略图-程序员宅基地

- scrapy爬虫框架_3.6.1 scrapy 的版本-程序员宅基地

- 微信支付——统一下单——java_小程序统一下单接口-程序员宅基地

- (已解决)报错 ValueError: Tensor conversion requested dtype float32 for Tensor with dtype resource-程序员宅基地

- 记录el-table树形数据,默认展开折叠按钮失效_eltable一刷新展开的子节点展开按钮消失-程序员宅基地

- 设计模式复习-桥接模式_csdn天使也掉毛-程序员宅基地

- CodeForces - 894A-QAQ(思维)_"qaq\" is a word to denote an expression of crying-程序员宅基地

- java毕业生设计移动学习网站计算机源码+系统+mysql+调试部署+lw-程序员宅基地

- 14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!_1秒笔记 高级-程序员宅基地

- 最新java毕业论文英文参考文献_计算机毕业论文javaweb英文文献-程序员宅基地